Assembly registers in 64-bit architecture

Categories:

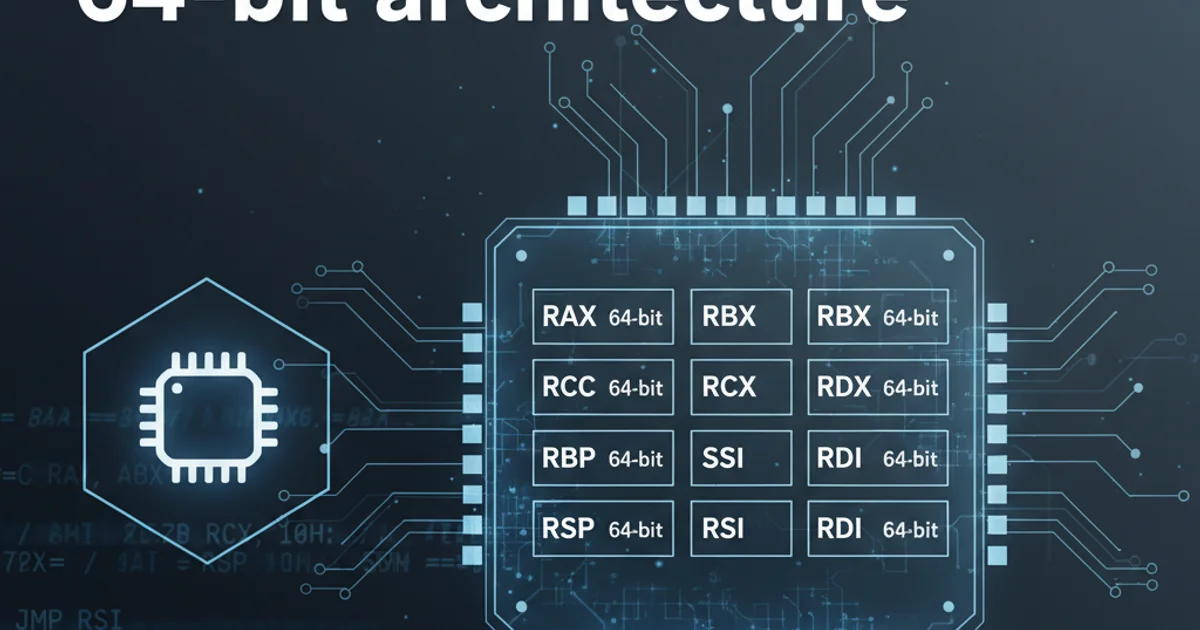

Understanding Assembly Registers in 64-bit x86-64 Architecture

Explore the fundamental role and organization of registers in 64-bit x86-64 assembly programming, contrasting them with their 32-bit counterparts.

Assembly language programming requires a deep understanding of a CPU's architecture, particularly its registers. Registers are small, high-speed storage locations directly within the CPU that are used to hold data and instructions during program execution. In the transition from 32-bit to 64-bit x86 architecture (x86-64), the register set underwent significant expansion and modification, providing more general-purpose registers and wider data paths. This article delves into the specifics of these registers, their naming conventions, and their primary uses in 64-bit environments.

General-Purpose Registers (GPRs)

The x86-64 architecture significantly expands the number and size of general-purpose registers compared to its 32-bit predecessor. While 32-bit x86 offered 8 GPRs (EAX, EBX, ECX, EDX, EBP, ESP, ESI, EDI), 64-bit x86-64 introduces 8 new registers (R8-R15) and extends the existing 8 to 64 bits (RAX, RBX, RCX, RDX, RBP, RSP, RSI, RDI). These registers are crucial for storing operands, memory addresses, and intermediate results during computation.

graph TD

subgraph 64-bit GPRs

RAX["RAX (Accumulator)"]

RBX["RBX (Base)"]

RCX["RCX (Counter)"]

RDX["RDX (Data)"]

RBP["RBP (Base Pointer)"]

RSP["RSP (Stack Pointer)"]

RSI["RSI (Source Index)"]

RDI["RDI (Destination Index)"]

R8["R8 (General Purpose)"]

R9["R9 (General Purpose)"]

R10["R10 (General Purpose)"]

R11["R11 (General Purpose)"]

R12["R12 (General Purpose)"]

R13["R13 (General Purpose)"]

R14["R14 (General Purpose)"]

R15["R15 (General Purpose)"]

end

subgraph 32-bit GPRs (Legacy)

EAX["EAX"]

EBX["EBX"]

ECX["ECX"]

EDX["EDX"]

EBP["EBP"]

ESP["ESP"]

ESI["ESI"]

EDI["EDI"]

end

RAX --- EAX

RBX --- EBX

RCX --- ECX

RDX --- EDX

RBP --- EBP

RSP --- ESP

RSI --- ESI

RDI --- EDI

style R8 fill:#f9f,stroke:#333,stroke-width:2px

style R9 fill:#f9f,stroke:#333,stroke-width:2px

style R10 fill:#f9f,stroke:#333,stroke-width:2px

style R11 fill:#f9f,stroke:#333,stroke-width:2px

style R12 fill:#f9f,stroke:#333,stroke-width:2px

style R13 fill:#f9f,stroke:#333,stroke-width:2px

style R14 fill:#f9f,stroke:#333,stroke-width:2px

style R15 fill:#f9f,stroke:#333,stroke-width:2pxExpansion of General-Purpose Registers from 32-bit to 64-bit x86-64. New 64-bit registers R8-R15 are highlighted.

Each 64-bit GPR can be accessed in smaller sizes: the lower 32 bits (e.g., EAX), the lower 16 bits (e.g., AX), and the lower 8 bits (e.g., AL). Additionally, the upper 8 bits of the lower 16-bit registers (e.g., AH, BH, CH, DH) are also accessible. For the new registers R8-R15, their lower 32, 16, and 8 bits are accessed as R8D, R8W, R8B, respectively, and so on.

; Example of accessing different sizes of RAX

mov rax, 0x1122334455667788 ; Move 64-bit value to RAX

mov eax, 0xAAAAAAAA ; Move 32-bit value to EAX (clears upper 32 bits of RAX)

mov ax, 0xBBBB ; Move 16-bit value to AX (affects lower 16 bits of RAX/EAX)

mov al, 0xCC ; Move 8-bit value to AL (affects lower 8 bits of RAX/EAX/AX)

mov ah, 0xDD ; Move 8-bit value to AH (affects bits 8-15 of RAX/EAX/AX)

; Example of accessing new 64-bit registers

mov r8, 0x123456789ABCDEF0 ; Move 64-bit value to R8

mov r9d, 0xDEADBEEF ; Move 32-bit value to R9D (clears upper 32 bits of R9)

mov r10w, 0xCAFE ; Move 16-bit value to R10W

mov r11b, 0xFE ; Move 8-bit value to R11B

Demonstrating register size access in x86-64 assembly.

mov eax, value), the upper 32 bits of the 64-bit register are automatically zero-extended. This is a crucial difference from 16-bit operations, which only affect the lower 16 bits and leave the upper bits unchanged. Be mindful of this behavior to avoid unexpected results.Special-Purpose Registers

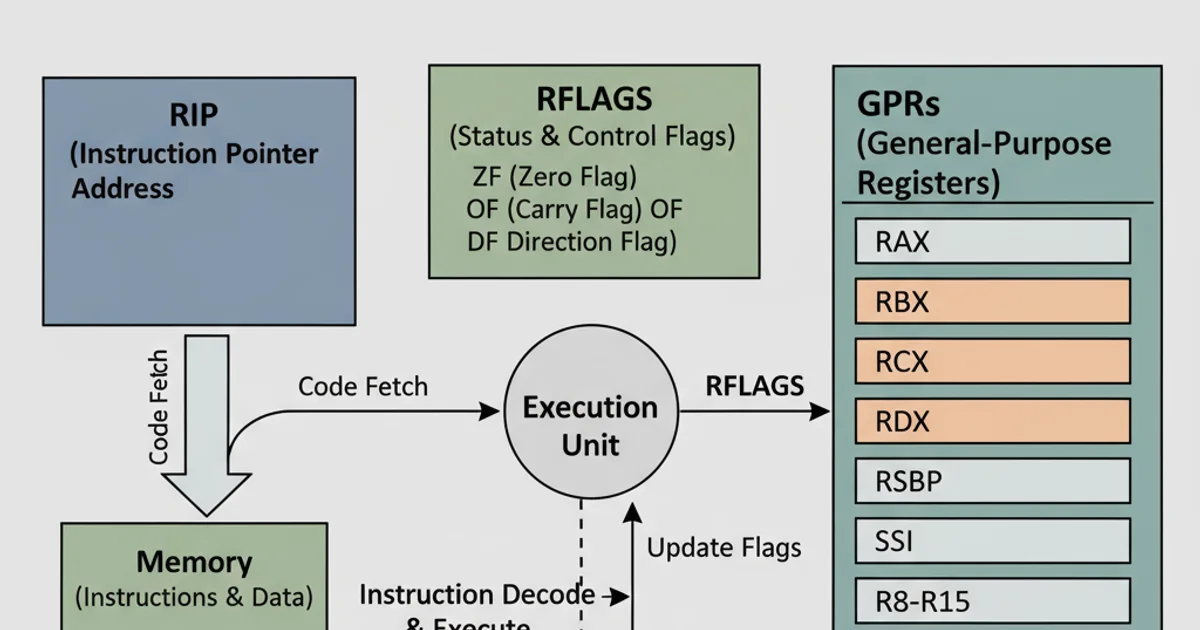

Beyond the general-purpose registers, x86-64 architecture includes several special-purpose registers vital for system operation, floating-point arithmetic, and vector processing. These include the Instruction Pointer (RIP), Flags Register (RFLAGS), Segment Registers, and various registers for floating-point (x87 FPU), Streaming SIMD Extensions (SSE), and Advanced Vector Extensions (AVX).

The Instruction Pointer (RIP) and Flags Register (RFLAGS) are critical for controlling program flow and status.

The 64-bit Instruction Pointer (RIP) holds the address of the next instruction to be executed, similar to EIP in 32-bit. The 64-bit RFLAGS register (formerly EFLAGS) contains status flags, control flags, and system flags that reflect the result of operations and control CPU behavior. While segment registers (CS, DS, SS, ES, FS, GS) still exist, their role is significantly diminished in 64-bit long mode, where a flat memory model is predominantly used, and FS/GS are often repurposed for thread-local storage.

Floating-Point and Vector Registers

Modern x86-64 CPUs include extensive support for floating-point and vector operations. The x87 FPU provides 80-bit floating-point registers (ST0-ST7) for legacy floating-point arithmetic. More commonly used are the SSE/AVX registers, which are 128-bit (XMM0-XMM15), 256-bit (YMM0-YMM15), and even 512-bit (ZMM0-ZMM31) for advanced vector processing. These registers are crucial for high-performance computing, graphics, and scientific applications.

flowchart LR

subgraph CPU Registers

GPRs["General Purpose Registers (RAX-R15)"]

RIP["Instruction Pointer (RIP)"]

RFLAGS["Flags Register (RFLAGS)"]

SegmentRegs["Segment Registers (CS, DS, SS, ES, FS, GS)"]

FPURegs["x87 FPU Registers (ST0-ST7)"]

SIMDRegs["SIMD/Vector Registers (XMM, YMM, ZMM)"]

end

GPRs --> RIP

GPRs --> RFLAGS

RIP --> ProgramExecution["Program Execution Flow"]

RFLAGS --> ConditionalLogic["Conditional Logic"]

SIMDRegs --> VectorOps["Vector Operations"]

FPURegs --> LegacyFPOps["Legacy FP Operations"]

style GPRs fill:#bbf,stroke:#333,stroke-width:2px

style SIMDRegs fill:#bfb,stroke:#333,stroke-width:2px

style FPURegs fill:#fbb,stroke:#333,stroke-width:2pxOverview of key register categories in x86-64 architecture.