Nop and Pipeline Hazards in this Assembly MIPS

Categories:

Understanding NOPs and Pipeline Hazards in MIPS Assembly

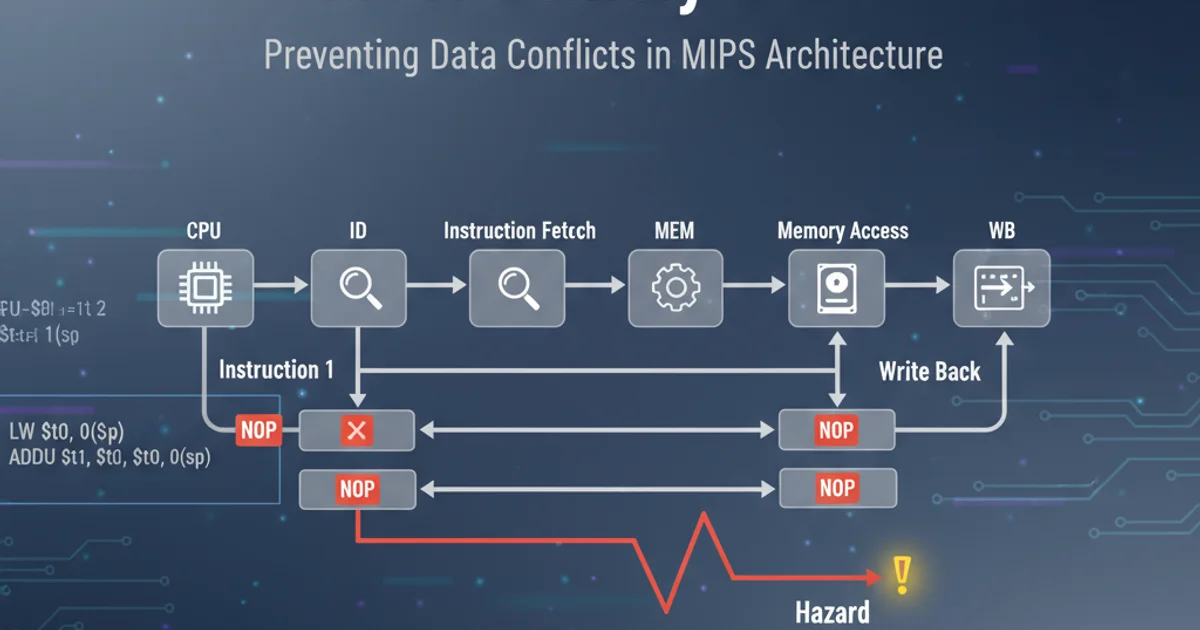

Explore the critical role of NOP instructions and how they mitigate pipeline hazards in MIPS assembly language programming, ensuring correct program execution.

MIPS (Microprocessor without Interlocked Pipeline Stages) architecture is known for its simplicity and efficiency, largely due to its pipelined design. However, pipelining introduces challenges known as hazards, which can lead to incorrect program behavior if not addressed. This article delves into the concept of NOP (No Operation) instructions and their essential role in resolving pipeline hazards in MIPS assembly.

The MIPS Pipeline: An Overview

A typical MIPS pipeline consists of five stages: Instruction Fetch (IF), Instruction Decode/Register Fetch (ID), Execute (EX), Memory Access (MEM), and Write Back (WB). Each stage works on a different instruction simultaneously, allowing for higher throughput. While this parallel execution is beneficial, it can cause dependencies between instructions to be violated, leading to hazards.

flowchart LR

IF[Instruction Fetch] --> ID[Instruction Decode/Register Fetch]

ID --> EX[Execute]

EX --> MEM[Memory Access]

MEM --> WB[Write Back]Simplified MIPS Pipeline Stages

Understanding Pipeline Hazards

Pipeline hazards occur when the execution of one instruction depends on the result of a previous instruction that has not yet completed its pipeline stages. There are three main types of hazards:

- Structural Hazards: Arise when two instructions require the same hardware resource at the same time.

- Data Hazards: Occur when an instruction tries to read a register that a previous instruction is still writing to.

- Control Hazards (Branch Hazards): Happen when the pipeline fetches instructions based on a branch that might or might not be taken, and the actual branch outcome is not known until later in the pipeline.

add $t0, $s0, $s1

sub $t2, $t0, $s3

Example of a data hazard: sub depends on $t0 from add.

NOP: The No Operation Instruction

A NOP instruction does nothing. In MIPS, it's typically encoded as sll $zero, $zero, 0, which shifts the zero register by zero bits and stores the result back into the zero register – effectively a no-op. NOPs are crucial for resolving pipeline hazards by introducing delays, allowing dependent instructions to complete their necessary stages before subsequent instructions attempt to use their results.

Resolving Data Hazards with NOPs

Consider the data hazard example above. The sub instruction needs the value of $t0 which is computed by the add instruction. Without intervention, sub might try to read $t0 before add has written its result back to the register file (WB stage). Inserting NOPs can delay sub until $t0 is ready.

sequenceDiagram

participant ADD as ADD $t0, $s0, $s1

participant NOP1 as NOP

participant NOP2 as NOP

participant SUB as SUB $t2, $t0, $s3

ADD->>ADD: IF

ADD->>ADD: ID

ADD->>ADD: EX

ADD->>ADD: MEM

ADD->>ADD: WB (writes $t0)

NOP1->>NOP1: IF

NOP1->>NOP1: ID

NOP1->>NOP1: EX

NOP1->>NOP1: MEM

NOP1->>NOP1: WB

NOP2->>NOP2: IF

NOP2->>NOP2: ID

NOP2->>NOP2: EX

NOP2->>NOP2: MEM

NOP2->>NOP2: WB

SUB->>SUB: IF

SUB->>SUB: ID (reads $t0)

Note over SUB: $t0 is now available from ADD's WB stageData Hazard Resolution using NOPs

add $t0, $s0, $s1

nop

nop

sub $t2, $t0, $s3

Data hazard resolved by inserting two NOPs.

Resolving Control Hazards with NOPs (Branch Delay Slots)

MIPS architecture typically has a branch delay slot. The instruction immediately following a branch instruction is always executed, regardless of whether the branch is taken or not. This instruction occupies the branch delay slot. If no useful instruction can be placed there, a NOP is used to fill the slot, preventing a control hazard.

beq $t0, $t1, Label

nop # Branch delay slot

add $s0, $s1, $s2 # This instruction might be skipped if branch is taken without NOP

Using NOP in a branch delay slot.

In summary, NOP instructions are a fundamental tool in MIPS assembly for managing pipeline hazards. While compilers and assemblers often handle these insertions automatically, understanding their purpose is crucial for debugging and optimizing MIPS code, especially in environments where manual optimization is necessary.